آرم از هسته های کورتکس X4 و A720 و A520 رونمایی کرد

آرم شرکتی است که تقریباً تمام هستههای پردازشی را که در نهایت در تلفن هوشمند اندرویدی شما استفاده شده، طراحی میکند و هر سال تکرارهای جدیدی را ارائه میکند که بعداً به چیپستهایی مانند اسنپدراگون پرچمدار آن سال یا پرچمدار بعدی مدیاتک دایمنسیتی راه پیدا میکنند.

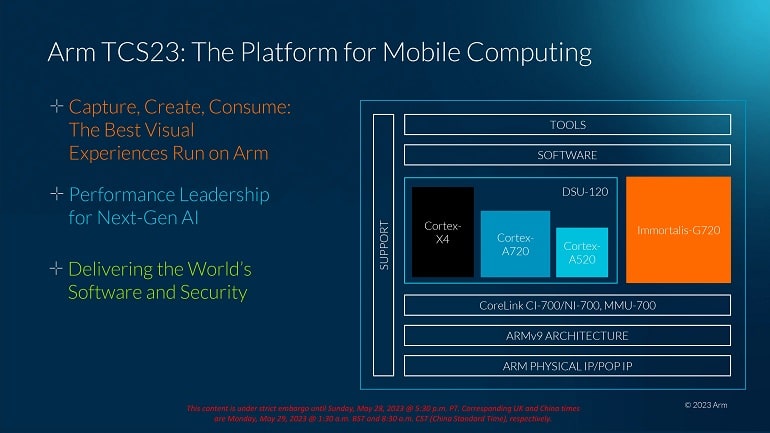

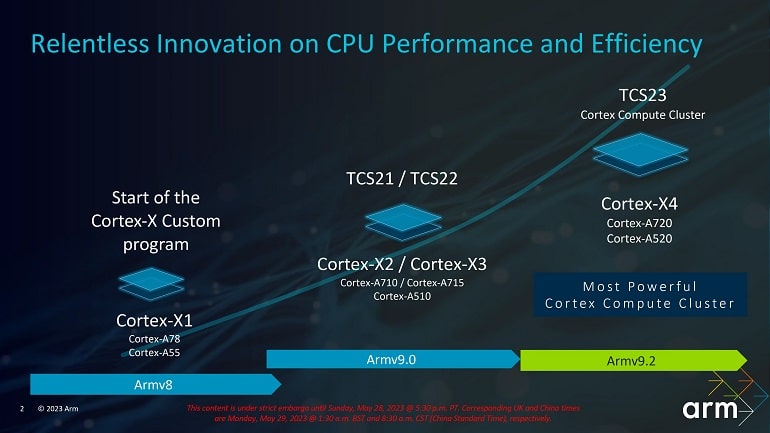

امسال یک هسته Cortex-X4 پرچمدار، یک هسته عملکرد Cortex-A720 و یک هسته کارآمد Cortex-A520 را معرفی کرده است. این هستهها اساس طرحهای سازگار با Arm v9.2 جدید شرکت و راهحل محاسبه مجموع این شرکت برای سال 2023 یا TCS23 را تشکیل میدهند. علاوه بر این، ما همچنین شاهد یک واحد مشترک DynamIQ و یک پردازشگر گرافیکی به روز شده Immortalis-G720 هستیم. هنوز بزرگتر یک انتقال کامل به محاسبات 64 بیتی است که هیچ یک از این هسته ها از 32 بیت پشتیبانی نمی کنند.

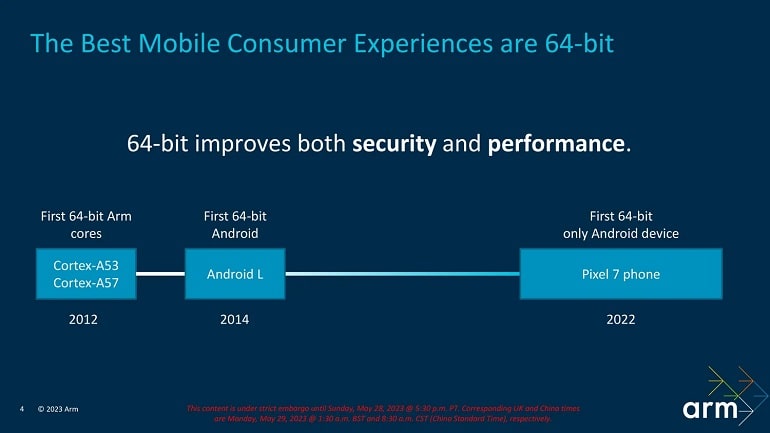

انتقال به نسخه 64 بیتی

هر سه هسته جدید جانشینان ریزمعماری سال گذشته هستند و در درجه اول بر معرفی IPC و افزایش بهره وری تمرکز دارند. یکی از بزرگترین تغییرات در Total Compute Solution امسال از آرم، انتقال تنها به 64 بیتی است. در حالی که A510R1 سال گذشته از حالت اجرای 32 بیتی AArch32 پشتیبانی می کرد، همانطور که A710 که سال گذشته با TCS22 راه اندازی شد، امسال، هسته های آرم فقط AArch64 هستند.

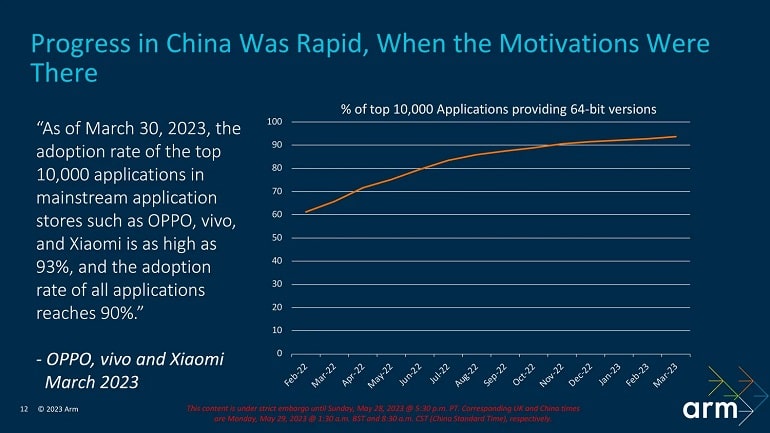

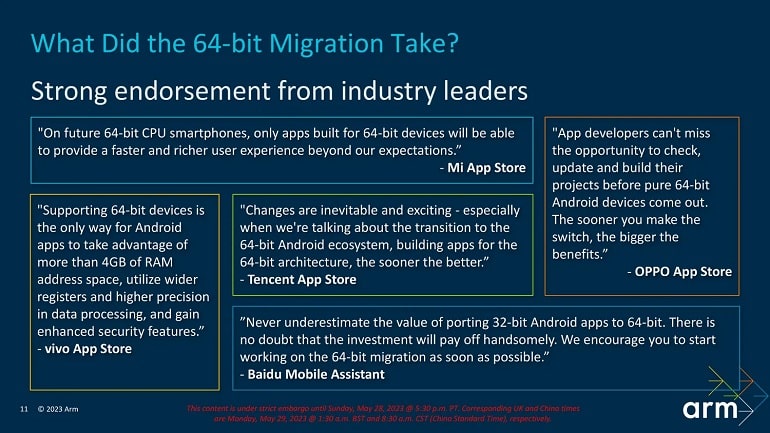

همانطور که Arm می گوید، انتقال 64 بیتی “ماموریت انجام شده” در نظر گرفته می شود. دلیل این امر این است که بازار اپلیکیشن های چینی چیزی است که بقیه صنعت را در دوران گذار عقب نگه داشته، اما اکثریت قریب به اتفاق اپلیکیشن های موجود در اپ استورهای چینی اکنون با 64 بیت سازگار هستند. دلیل تأخیر فقدان یک اکوسیستم برنامه یکسان بود، به این معنی که اپ استورهای مختلف به استانداردهای متفاوتی از توسعه دهندگان نیاز داشتند.

از آنجایی که Arm با فروشگاه های برنامه های مختلف در چین کار کرده، اما، همراه با هشدارهای مکرر مبنی بر اینکه تغییری رخ خواهد داد، این فروشگاه های برنامه توسعه دهندگان را نیز تشویق به تغییر کرده اند. به نظر می رسد زمان آن فرا رسیده است که این انتقال به طور کامل انجام شود، و به هر حال چند ماه دیگر تا زمانی که این هسته های Arm را در چیپست های جدید ببینیم، باقی مانده است.

Cortex-X4: عملکرد بیشتر و کارایی بهتر

هستههای سری X آرم چند سال پیش از سری A خود جدا شدند، با این فلسفه که هستهای قدرتمند است که در صورت نیاز میتواند کمی قدرت بیشتری مصرف کند. به طور معمول، سازندگان چیپست تنها یک یا دو مورد از اینها را حداکثر استفاده می کنند، زیرا آنها تشنه انرژی هستند، حتی با وجود قابلیت هایی که دارند.

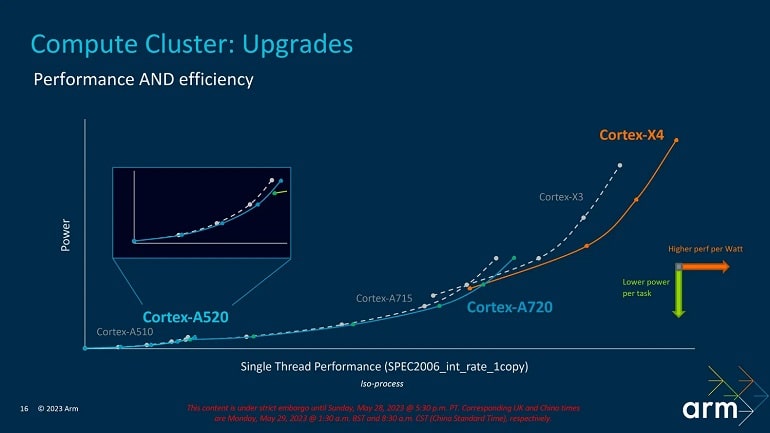

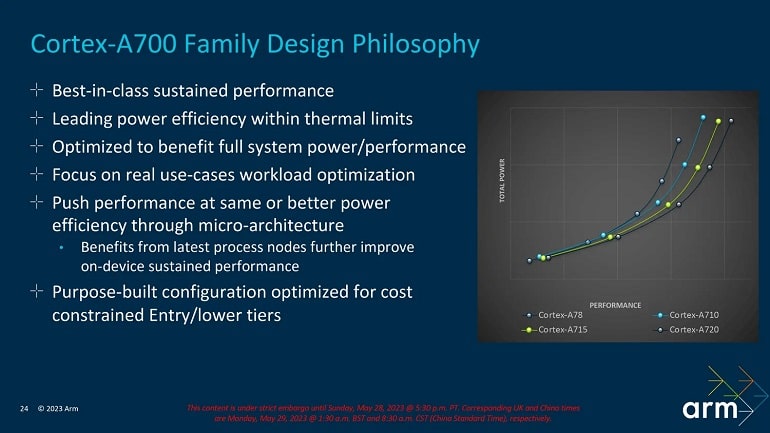

همانطور که از نمودار بالا می بینید، Cortex-X4 قدرتمندترین هسته Arm است، اما این قابلیت های محاسباتی به قیمت مصرف انرژی است. Cortex-X4 مشابه X3 سال گذشته است و همانطور که Arm می گوید، حتی می تواند با فرکانس های مشابه هسته سال گذشته کار کند و تا 40 درصد انرژی کمتری مصرف کند. این هسته از نظر اندازه فیزیکی کمتر از 10 درصد بزرگتر است و کارآمدترین هسته Cortex-X تا کنون ساخته شده است.

در مورد اینکه این پیشرفتهای IPC از کجا میآیند، تعدادی بهبود فرانت اند و بک اند در X4 وجود دارد. در آن پیشرفتهای فرانتاند، حجم زیادی از کار برای بازنویسی و بهبود پیشبینیهای شاخهها انجام شد، زیرا پیشبینیهای نادرست شاخه پرهزینه و از نظر عملکرد هستند. Arm همچنین قول داده که اندازه کش 2 مگابایتی L2 عملکرد بالاتری را ارائه می دهد (نه در معیارها بلکه در استفاده در دنیای واقعی).

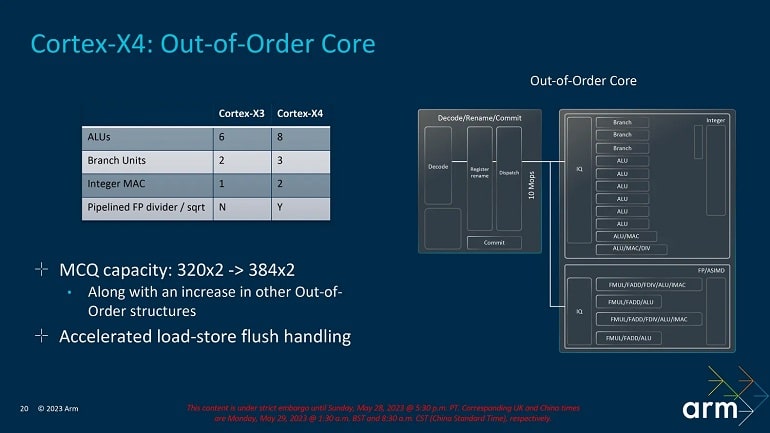

تعداد واحدهای منطقی محاسباتی (ALU) هسته جدید Cortex-X4 از 6 به 8 افزایش یافته و یک واحد شاخه اضافی (در مجموع 3 عدد)، یک واحد Multiply-Acumulatator به آن اضافه شده است. در مورد قسمت بک اند نیز، تعدادی پیشرفت نیز وجود دارد. تولید آدرس Load-Store از سه دستورالعمل به چهار دستورالعمل در هر چرخه رسیده است. همچنین یک بافر دو برابری ترجمه در L1 همراه با بهبودهای مربوط به تضاد بانکی وجود دارد.

همه اینها با هم ترکیب می شوند تا عملکرد چشمگیری را در Arm’s Cortex-X4 افزایش دهند. در مجموع، می توانید انتظار بهبود عملکرد متوسط 15 درصد با Cortex-X4 را داشته باشید. در منحنی قدرت و عملکرد مشترک آرم، X4 در عملکرد و مصرف انرژی از X3 جلوتر است. به عبارت دیگر، این بهبود عملکرد 15 درصدی با مصرف انرژی بسیار قابل توجهی همراه است.

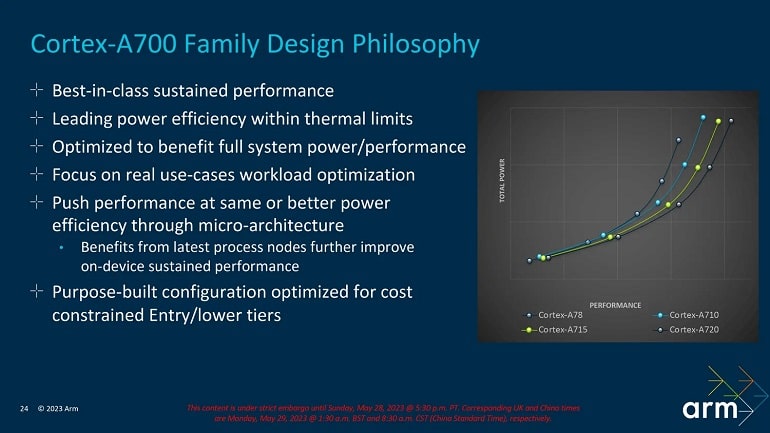

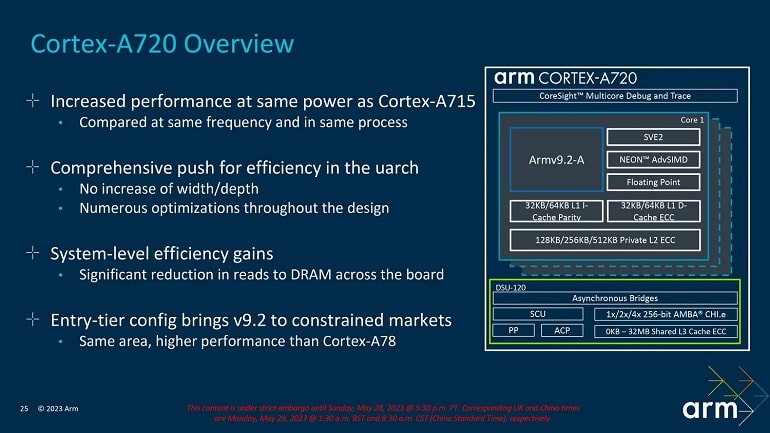

Cortex-A720: متعادل کردن عملکرد و مصرف انرژی

در حالی که هسته های سری X آرم به طور معمول اجازه می دهند کمی بیشتر کار کنند، سری هسته های A معمولاً هدفشان متعادل کردن مصرف انرژی در مقابل عملکرد است. با Cortex-A720، آرم نوید یک هسته کارآمدتر 20٪ با افزایش عملکرد با همان قدرت A715 از سال گذشته را می دهد.

در مورد اینکه پیشرفتهای A720 امسال از کجا میآیند، بیشتر آنها در بخش فرانت اند قرار دارند. خطوط لوله با حذف یک چرخه از موتور پیشبینی نادرست انشعاب کوتاه شدهاند و گفته میشود که این کاهش یک چرخه باعث افزایش 1 درصدی در معیارها میشود. معیارها معمولاً منجر به کمترین پیشبینی نادرست شاخه میشوند، به این معنی که این امر احتمالاً عملکرد کلی دنیای واقعی را به میزان قابل توجهی (اما تا حد زیادی غیرقابل اندازهگیری) بهبود میبخشد.

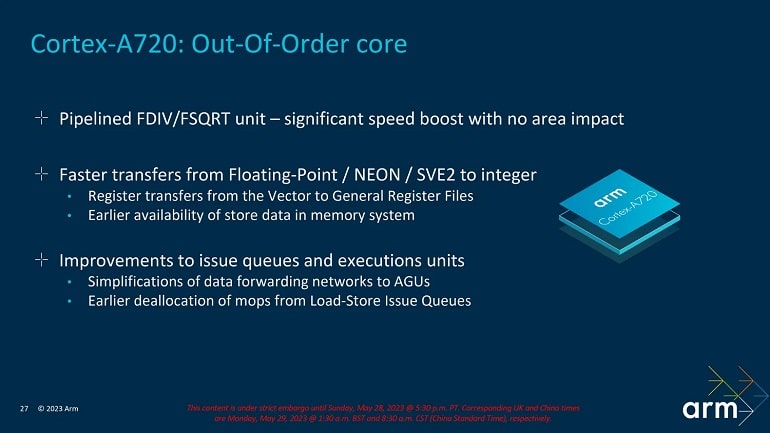

در هسته خارج از نظم، تعدادی از پیشرفتهای ساختاری را میبینیم که به بهبود عملکرد کمک میکنند بدون اینکه بر ناحیه اشغال شده توسط هسته یا کارایی آن تأثیر بگذارند. برای شروع، درست مانند X4، تقسیم نقطه شناور و عملیات ریشه مربع در حال حاضر خط لوله انجام می شود. همچنین انتقال سریعتری از اعداد ممیز شناور، NEON و SVE2 به اعداد صحیح و سایر پیشرفتهای کلی برای سرعت بخشیدن به پردازش وجود دارد.

Arm نمودار بالا را به اشتراک گذاشت تا نشان دهد که چگونه A720 در عملکرد و کارایی با A715 سال گذشته مقایسه می شود، جایی که فرآیند ISO و فرکانس ISO در SPECint_base2006 استفاده می شود. اندازههای حافظه کش نیز ثابت میمانند، بنابراین مقایسهای بین سیب به سیب است. از نظر مصرف انرژی، A720 بسیار مطابق با مدل سال گذشته است، اگرچه عملکرد کمی بیشتر در همان سطوح قدرت دارد. با A720، مانند X4، به نظر میرسد Arm بیشتر بر روی برجسته کردن عملکرد بهتر از محدودیتهای برق سال گذشته تمرکز دارد تا اینکه به طور مداوم قدرتی را که این هستهها قادر به انجام آن هستند افزایش دهد.

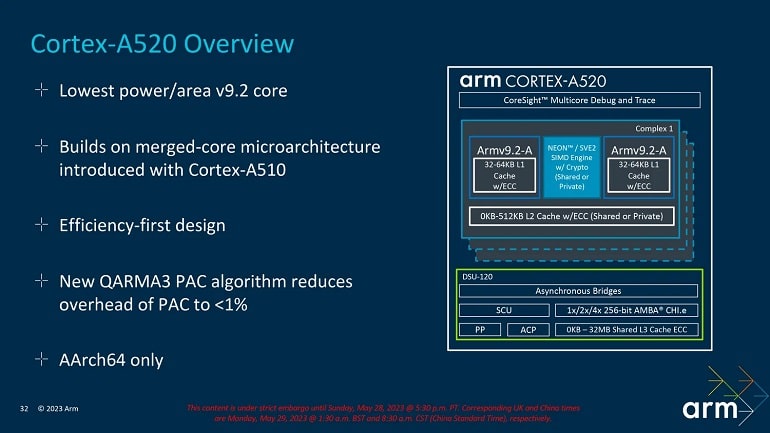

Arm Cortex A520: کاهش کارایی

البته وقتی صحبت از هسته های Arm به میان می آید، همه چیز در مورد عملکرد نیست. با توجه به اینکه سری X همه چیز را در قدرت محاسباتی خام قرار می دهد و نیازهای محاسباتی و توان مصرفی A7xx را متعادل می کند، سری A5xx صرفاً بر روی پردازش کارآمد تمرکز می کند. این کمترین قدرت در هر منطقه هسته Arm v9.2 است و بر اساس همان معماری هسته ادغام شده ای است که با A510 معرفی کردیم.

معنی این معماری هسته ادغام شده این است که برخی از منابع را می توان بین دو هسته به اشتراک گذاشت، جایی که دو هسته را می توان در یک “کمپلکس” گروه بندی کرد. حافظه کش L2، بافر ترجمه L2 و مسیرهای داده برداری در این مجموعه مشترک هستند. برای روشن بودن، این بدان معنا نیست که باید به دو هسته تقسیم شود و یک مجموعه یک هسته ای را می توان برای حداکثر کارایی مونتاژ کرد.

در واقع، یکی از طرحبندیهای هسته TCS2023 Arm که به ما نشان داد شامل یک هسته X4، پنج هسته A720 و سه هسته A520 بود، به این معنی که حداقل یک هسته A520 در انزوا قرار دارد. A520 اولین طراحی با کارایی است، و مانند هسته های دیگر، Arm تا حد زیادی بر روی بهبود این راندمان در نقاط قدرت مشابه نسل گذشته تمرکز کرده است.

این شامل بهبود پیشبینیهای شاخه و همچنین حذف یا کوچکشدن برخی از ویژگیهای عملکرد است. این عملکرد از طریق کارایی بیشتر در نتیجه بازیابی شد. همچنین جالب است که Arm سومین ALU را که در A510 وجود داشت حذف کرده و باعث صرفه جویی در قدرت در صدور منطق و نتایج ارسال شده است.

در نتایج دنیای واقعی، به نظر می رسد که A520 به اندازه A720 و X4 نسبت به مدل های قبلی خود جهش بزرگی ندارد. بسیاری از قابلیتهای آن در فواصل توان کمتر با A510 از نمودار بالا همپوشانی دارند، و تنها در سطوح بالای عملکرد شاهد افزایش بازدهی هستیم. تفاوت عملکرد و قدرت بین دو هسته امیدوارکننده است، اما مشخص نیست که آیا در مقایسه A520 با A510 مزایای واقعی واقعی را مشاهده خواهیم کرد یا خیر. از این گذشته، اندازه گیری درست تفاوت عملکرد و کارایی بین این دو در دنیای واقعی دشوار است.

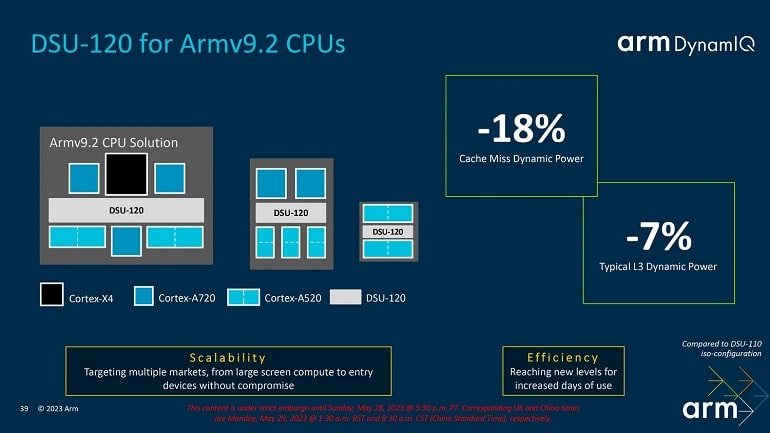

DSU-120: تا 14 هسته حسن محاسباتی

واحد مشترک DynamIQ یا DSU، یک یا چند هسته را با یک سیستم حافظه L3، منطق کنترل و رابط های خارجی به منظور تشکیل یک خوشه چند هسته ای ادغام می کند. این اساساً پارچه Arm است که به همه این هستهها اجازه میدهد با یکدیگر ارتباط برقرار کنند و منابع را به اشتراک بگذارند، و به همین دلیل، برای هر سازنده چیپست که به دنبال ساخت تراشه با طرحهای هسته Arm است، یک قطعه نسبتاً مهم از پازل است.

با ساخت DSU-110، آرم تعدادی بهبود در DSU-120 ایجاد کرده که به نفع کل چیپ موجود در آن است. برای شروع، در حال حاضر حداکثر 14 هسته در هر کلاستر (از 12) و پشتیبانی از حداکثر 32 مگابایت حافظه کش L3 وجود دارد. همچنین کارایی را در تعدادی از زمینههای کلیدی، از جمله در صورت از دست دادن حافظه کش ، بهبود میبخشد، در حالی که نشت برق را نیز کاهش میدهد.

به نوعی، آرم DSU ستون فقرات TCS23 است، زیرا اساس نحوه تعامل هر یک از این هسته ها با یکدیگر و به اشتراک گذاری داده ها را تشکیل می دهد. هر گونه بهبودی در اینجا به نفع کل خوشه خواهد بود، اما به نظر می رسد بیشتر تغییرات مربوط به مصرف برق و کارایی است.