TSMC جدیدترین دستگاه لیتوگرافی EUV شرکت ASML را در سال جاری دریافت میکند

ASML (Advanced Semiconductor Materials Lithography) یک شرکت هلندی است که به طراحی و تولید دستگاههای لیتوگرافی برای صنعت نیمهرسانا میپردازد. این دستگاهها یکی از مهمترین تجهیزات در ساخت تراشهها به شمار میروند. دسترسی به تکنولوژی پیشرفته لیتوگرافی ASML یکی از دلایل اصلی موفقیت چشمگیر TSMC به عنوان یک تولیدکننده قراردادی تراشه است که با بزرگترین شرکتهای صنعت نظیر انویدیا و کوالکام همکاری دارد.

به تازگی اعلام شده که ASML قصد دارد تا پایان سال جاری میلادی، پیشرفتهترین دستگاه لیتوگرافی خود را که ارزش آن حدود 380 میلیون دلار (حدود 2.753 میلیارد یوان) است، به TSMC ارسال کند. راجر داسن، مدیر مالی ASML، در یک تماس کنفرانسی اخیر فاش کرد که دو مشتری بزرگ این شرکت، TSMC و اینتل، در سال 2024 به تکنولوژی لیتوگرافی پیشرفته (high-NA) EUV دست خواهند یافت.

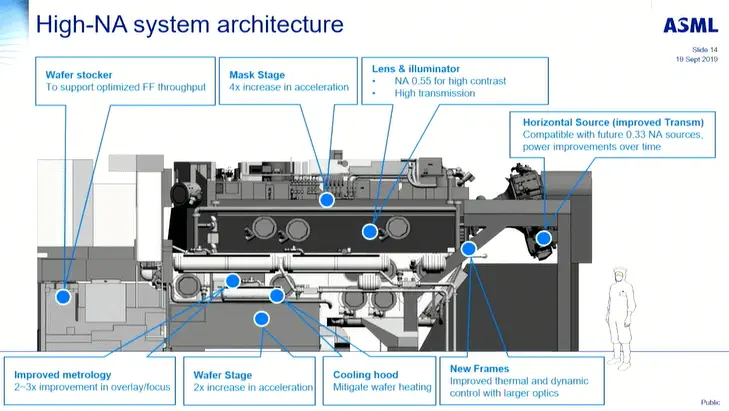

گزارشها حاکی از آن است که ASML اولین دستگاه تجاری لیتوگرافی high-NA EUV را به اینتل تحویل داده است. اولین واحد این دستگاه در اواخر دسامبر به کارخانهای در اورگان تحویل داده شد. زمان دقیق دریافت جدیدترین و پیشرفتهترین ابزار ASML توسط TSMC هنوز مشخص نیست. انتظار میرود تکنولوژی لیتوگرافی high-NA اندازه ترانزیستورها را 66 درصد کاهش دهد. بنابراین، این تکنولوژی میتواند به تولیدکنندگان تراشه کمک کند تا تعداد بیشتری ترانزیستور در یک قطعه سیلیکون با اندازه مشابه قرار دهند.

واضح است که تعداد ترانزیستورها تنها عامل مهم نیست (مواردی نظیر بهرهوری انرژی نیز حائز اهمیت است) اما بهرهوری انرژی نیز با کاهش اندازه بهبود مییابد. گزارشها نشان میدهد که سیستم high-NA EUV به عدد دیافراگم عددی (NA) 0.55 دست مییابد. در مقایسه با سیستمهای EUV قبلی که به لنزهای با دیافراگم عددی 0.33 مجهز بودند، دقت بیشتری را ارائه میدهد و امکان طراحیهای پیچیدهتری روی سیلیکون را فراهم میکند.

این دستگاه نیز 30 درصد بزرگتر از پیشینیان خود است که از قبل آنقدر بزرگ بودند که برای حمل آنها نیاز به سه فروند هواپیمای بویینگ 747 بود. در مورد TSMC، توسعه گرههای 2 نانومتری به خوبی در حال پیشرفت است. این شرکت قصد دارد در سهماهه دوم سال 2025 توسعه فرآیند N3X و N2 را آغاز کند. تولید انبوه N2P و A16 از سهماهه دوم سال 2026 آغاز خواهد شد. فرآیند 2 نانومتری این شرکت از FETهای Gate-all-around (GAAFET) استفاده خواهد کرد. TSMC انتظار دارد فرآیند 2 نانومتری آن بهبود عملکرد 10 تا 15 درصدی و کاهش مصرف انرژی 25 تا 30 درصدی را به همراه داشته باشد.