سامسونگ با Synposys برای بهینه سازی تراشه های 2 نانومتری همکاری می کند

شرکت Synopsys اعلام کرده است که ابزارهای جریان طراحی و مالکیت معنوی (IP) آن برای فرآیند ساخت 2 نانومتری Samsung Foundry آماده است. سامسونگ اخیرا اعلام کرده که برای تولید انبوه تراشه های نیمه هادی 2 نانومتری در سال آینده آماده خواهد بود و این روند در سال 2027 بیشتر بهبود خواهد یافت.

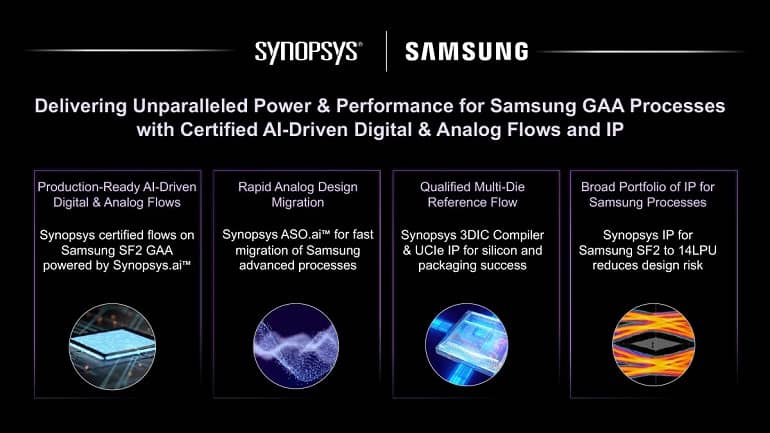

شرکتهای طراحی تراشه و مشتریانی که علاقهمند به ساخت تراشههای خود با استفاده از فرآیند 2 نانومتری Samsung Foundry هستند، خوشحال میشوند که بدانند ابزارهای طراحی دیجیتال و آنالوگ مبتنی بر هوش مصنوعی Synopsys گواهینامهای را برای آن گره فرآیند با چندین نوار چسب دریافت کردهاند.

Synopsys.ai مجموعه تمام پشته اتوماسیون طراحی الکترونیکی (EDA) است که مهاجرت طراحی آنالوگ، PPA و بهره وری را برای گره فرآیند 2 نانومتری Gate All Around (GAA) سامسونگ Foundry بهبود می بخشد. راه حل بهینه سازی مشترک فناوری طراحی مبتنی بر هوش مصنوعی (DTCO) Synopsys فرآیند 2 نانومتری سامسونگ را بهینه کرده و منطقه، عملکرد و بهره وری انرژی را بهبود می بخشد.

ابزار Synopsys DSO.ai برای بهره وری طراحی و بهینه سازی PPA استفاده می شود، در حالی که Synopsys ASO.ai برای مهاجرت سریعتر طراحی آنالوگ استفاده می شود. این فرآیندها برای انتقال طرحها از FinFET به معماری GAA اعمال شدهاند، به این معنی که مشتریان میتوانند طرحهای تراشههای خود را که برای فرآیند 8 نانومتری FinFET (یا قدیمیتر) استفاده میشوند به فرآیند جدید GAA 2 نانومتری منتقل کنند.

شرکتهای تولید تراشه میتوانند از ابزارهای Synopsys برای توسعه تکنیکهای جدید طراحی تراشه، از جمله Backside Power Routing، متدولوژی آگاه از اثر طرحبندی محلی، و طراحی سلول نانوصفحه، برای بهبود کارایی و عملکرد بالاتر با فرآیند SF2 استفاده کنند. گره فرآیند SF2Z سامسونگ Foundry می تواند عملکرد، قدرت و مساحت را بیشتر (20 درصد) بهبود بخشد.

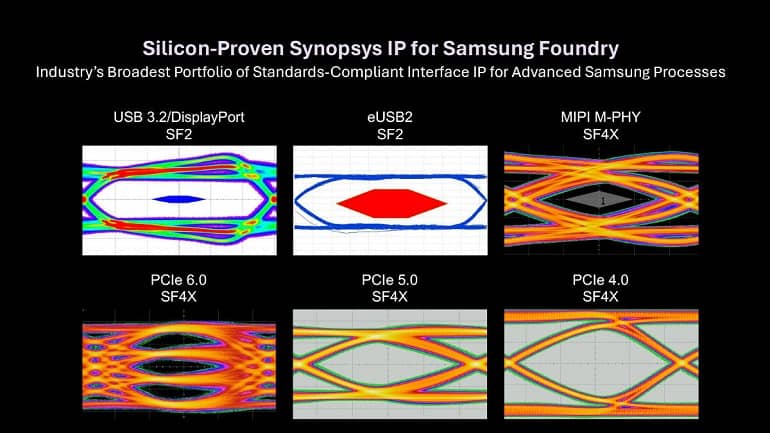

Synopsys UCIe IP برای حذف تراشه ها با استفاده از فرآیندهای SF2 و SF4x برای ادغام سریعتر چیپلت ها در بسته های multi-die استفاده شده است. تأخیر، قدرت و اتصال multi-die نیز در فرآیند SF5A بهبود یافته است. کامپایلر 3DIC Synopsys را می توان برای ادغام ناهمگن 2.5 بعدی و سه بعدی و بسته بندی پیشرفته استفاده کرد. علاوه بر این، Synopsys فاش کرده است که از همان راه حل DTCO برای بهینه سازی گره فرآیند 1.4 نانومتری Samsung Foundry (SF1.4) نیز استفاده خواهد شد.