IBM از پردازنده Telum II و Spyre Accelerator رونمایی کرد

IBM در کنفرانس Hot Chips 2024 جزئیات معماری پردازندههای آیندهی خود، IBM Telum II و IBM Spyre Accelerator را اعلام کرد. این فناوریهای نوین به گونهای طراحی شدهاند که قابلیت پردازشی سیستمهای مرکزی نسل بعدی IBM Z را افزایش داده و به تسریع در استفاده از مدلهای سنتی و مدلهای هوش مصنوعی با زبانهای بزرگ از طریق روشهای جدید گروهی هوش مصنوعی کمک میکنند.

با توجه به اینکه بسیاری از پروژههای هوش مصنوعی مولد که از مدلهای زبان بزرگ (LLM) استفاده میکنند، در حال گذار از مرحله اثبات مفهوم به تولید هستند، تقاضا برای راهحلهای کارآمد، ایمن و قابل مقیاسگذاری به عنوان اولویتهای اصلی مطرح شده است.

مطالعات منتشر شده توسط مورگان استنلی در ماه آگوست نشان میدهد که تقاضا برای انرژی مورد نیاز برای هوش مصنوعی مولد در چند سال آینده سالانه 75 درصد افزایش خواهد یافت، به طوری که پیشبینی میشود در سال 2026 میزان مصرف انرژی به اندازه کشور اسپانیا در سال 2022 باشد.

تصمیمات معماری بسیاری از مشتریان IBM برای پشتیبانی از مدلهای فونداسیون با اندازه مناسب و رویکردهای ترکیبی، طراحی شده برای بار کاری هوش مصنوعی، اهمیت فزایندهای پیدا کردهاند. نوآوریهای کلیدی که امروز معرفی شدند، شامل موارد زیر است.

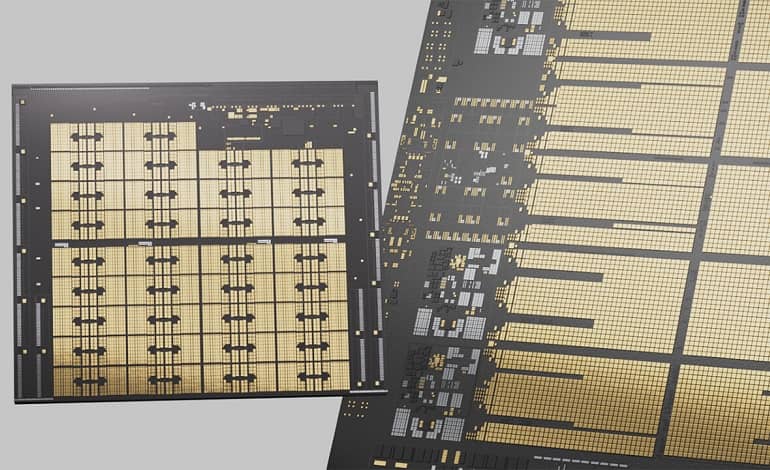

پردازنده IBM Telum II

تراشه جدید IBM که برای تأمین انرژی نسل بعدی سیستمهای IBM Z طراحی شده، دارای فرکانس بالاتر، ظرفیت حافظه افزایش یافته، 40 درصد رشد در حافظه کش و هستهای مجتمع برای شتابدهی به هوش مصنوعی، به علاوه یک واحد پردازش داده (DPU) که به طور هماهنگ متصل شده است. این تراشه، نسل اول Telum را دنبال میکند. انتظار میرود که پردازنده جدید از راهحلهای محاسباتی سازمانی برای مدلهای زبان بزرگ (LLM) پشتیبانی کند و به نیازهای معاملات پیچیده صنعت پاسخ دهد.

واحد پردازش داده کاملاً جدید (DPU) در تراشه پردازنده Telum II برای تسریع پروتکلهای پیچیده IO برای شبکه و ذخیرهسازی در پردازنده مرکزی طراحی شده است. DPU عملیات سیستم را تسهیل میکند و میتواند به بهبود عملکرد اجزای کلیدی کمک کند.

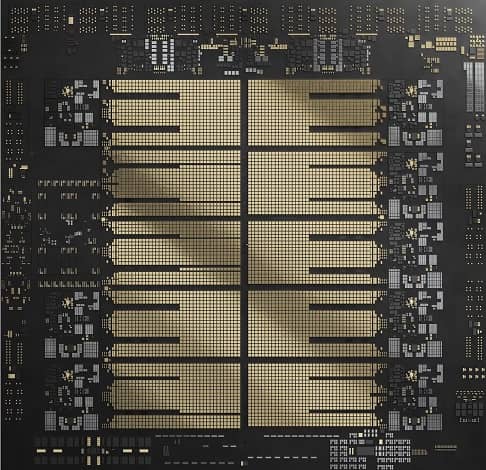

IBM Spyre Accelerator

تراشههای Telum II و Spyre با همکاری یکدیگر، یک معماری قابل انعطاف را برای پشتیبانی از روشهای متنوع مدلسازی هوش مصنوعی فراهم میکنند، که شامل ترکیب چندین مدل یادگیری ماشین و یادگیری عمیق AI با رمزگذارهای LLM است. با بهرهگیری از قوتهای معماری هر مدل، هوش مصنوعی مجموعه میتواند نتایجی دقیقتر و قویتر نسبت به مدلهای مستقل ارائه دهد. تراشه شتابدهنده IBM Spyre که در کنفرانس Hot Chips 2024 معرفی شد، بهعنوان یک افزونه قابل ارائه خواهد بود.

هر تراشه شتابدهنده از طریق یک آداپتور PCIe با توان 75 وات متصل میشود و بر پایه فناوریهای توسعهیافته توسط IBM Research است. مانند دیگر کارتهای PCIe، شتاب دهنده Spyre Accelerator قابلیت انطباق با نیازهای متفاوت کلاینت ها را دارد. پردازندههای Telum II و شتابدهنده IBM Spyre توسط Samsung Foundry، شریک تولیدی قدیمی IBM، ساخته خواهند شد و بر اساس فرآیند 5 نانومتری پیشرفته و کارآمد آنها تولید میشوند.

با همکاری نزدیک، این محصولات از طیف گستردهای از کاربردهای پیشرفته مبتنی بر هوش مصنوعی که برای ایجاد ارزش تجاری و مزیتهای رقابتی طراحی شدهاند، پشتیبانی خواهند کرد. با استفاده از روشهای ترکیبی هوش مصنوعی، مشتریان قادر خواهند بود نتایجی سریعتر و دقیقتر در پیشبینیهای خود کسب کنند.

مشخصات و معیارهای عملکرد

Telum II processor: پردازندهای با هشت هسته و کارایی بالا که با فرکانس 5.5 گیگاهرتز کار میکند، دارای 36 مگابایت حافظه کش L2 در هر هسته است و ظرفیت کش روی تراشه را 40 درصد افزایش داده تا به مجموع 360 مگابایت برسد. حافظه کش مجازی L4 با ظرفیت 2.88 گیگابایت در هر کشوی پردازنده، 40 درصد بیشتر از نسل قبلی است. شتابدهنده هوش مصنوعی یکپارچه، استنباط هوش مصنوعی را با تأخیر کم و توان عملیاتی بالا ممکن میسازد، که به عنوان مثال، قابلیت تشخیص تقلب را در تراکنشهای مالی بهبود میبخشد و ظرفیت محاسباتی هر تراشه را چهار برابر نسل قبلی افزایش میدهد.

واحد شتاب I/O جدید DPU در تراشه Telum II ادغام شده و برای بهبود مدیریت دادهها با افزایش 50 درصدی تراکم ورودی/خروجی طراحی شده است. این پیشرفت، کارایی و مقیاسپذیری کلی سیستم IBM Z را افزایش میدهد و آن را برای مدیریت بار کاری هوش مصنوعی در مقیاس بزرگ و برنامههای کاربردی دادههای فشرده مناسب برای کسبوکارهای امروزی میسازد.

Spyre Accelerator: یک شتابدهنده درجهیک سازمانی طراحی شده که قابلیتهای مقیاسپذیر را برای مدلهای پیچیده هوش مصنوعی و کاربردهای هوش مصنوعی مولد فراهم میکند. این شتابدهنده دارای حداکثر یک ترابایت حافظه است و برای کار مداوم در میان 8 کارت یک کشوی معمولی I/O ساخته شده تا از بارهای کاری مدلهای هوش مصنوعی در سراسر پردازنده مرکزی پشتیبانی کند، در حالی که برای مصرف بیش از 75 وات در هر کارت طراحی شده است. هر چیپ شامل 32 هسته محاسباتی است که از دادههای int4، int8، fp8 و fp16 برای برنامههای هوش مصنوعی با تأخیر کم و توان عملیاتی بالا پشتیبانی میکند.

پردازنده Telum II به عنوان پردازنده مرکزی، نسل بعدی پلتفرمهای IBM Z و IBM LinuxONE را تأمین خواهد کرد. انتظار میرود که در سال 2025 برای مشتریان IBM Z و LinuxONE در دسترس باشد. شتابدهنده IBM Spyre، که در حال حاضر در مرحله پیشنمایش فناوری قرار دارد، نیز انتظار میرود که در سال 2025 در دسترس قرار گیرد.